# » User Guide «

CP3010-SA

Doc. ID: 1056-1693, Rev. 2.1

Date: April 27, 2022

# **Revision History**

| Revision | Brief Description of Changes                                | Date of Issue |

|----------|-------------------------------------------------------------|---------------|

| 1.0      | Initial issue                                               | 4-Nov-2014    |

| 2.0      | General update, made changes to Chapter 1.5 and Chapter 5.1 | 25-Aug-2016   |

# **Imprint**

Kontron Europe GmbH may be contacted via the following:

MAILING ADDRESS TELEPHONE AND E-MAIL

Kontron Europe GmbH +49 (0) 800-SALESKONTRON Lise-Meitner-Straße 3-5 sales@kontron.com 86156 Augsburg, Germany

For further information concerning other Kontron products, please visit our Internet website: www.kontron.com.

### Disclaimer

Copyright © 2016 Kontron AG. All rights reserved. All data is for information purposes only and not guaranteed for legal purposes. Information has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. Kontron and the Kontron logo and all other trademarks or registered trademarks are the property of their respective owners and are recognized. Specifications are subject to change without notice.

# **Contents**

| Revision  | History                                  | 2  |

|-----------|------------------------------------------|----|

| Imprint . |                                          | 2  |

| Disclaime | er                                       | 2  |

| Contents  | 5                                        | 3  |

| Tables    |                                          | 7  |

| Figures . |                                          | 9  |

| Warranty  | /                                        | 10 |

| Proprieta | ary Note                                 | 10 |

| Trademar  | rks                                      | 10 |

| Environm  | nental Protection Statement              | 10 |

| 1         | Introduction                             | 11 |

| 1.1       | Board Overview                           | 11 |

| 1.2       | System Expansion Capabilities            | 12 |

| 1.2.1     | CP3010-HDD Extension Module (8 HP)       | 12 |

| 1.2.2     | CP-RIO3-04 Rear Transition Module        | 12 |

| 1.3       | Board Diagrams                           | 12 |

| 1.3.1     | Functional Block Diagram                 | 13 |

| 1.3.2     | Front Panel                              | 14 |

| 1.3.3     | Board Layout                             | 15 |

| 1.4       | Technical Specification                  | 16 |

| 1.5       | Standards                                | 20 |

| 1.6       | Related Publications                     | 21 |

| 2         | Functional Description                   | 22 |

| 2.1       | Processor                                | 22 |

| 2.1.1     | Integrated Processor Graphics Controller | 22 |

| 2.2       | Memory                                   | 23 |

| 2.3       | Watchdog Timer                           | 23 |

| 2.4       | Battery                                  | 23 |

| 2.5       | Flash Memory                             | 23 |

| 2.5.1     | SPI Boot Flash for uEFI BIOS             | 23 |

| 2.5.2     | SATA Flash                               | 24 |

| 2.6       | Trusted Platform Module 1.2              | 24 |

| 2.7       | Board Interfaces                         | 24 |

| 2.7.1     | Front Panel LEDs                         | 24 |

| 2.7.1.1   | System Status LEDs                       | 24 |

| 2.7.1.2   | General Purpose LEDs                     | 25 |

| 2.7.2     | USB Interfaces                           | 26 |

| 2.7.3     | DisplayPort Interfaces                   | 26 |

| 2.7.4      | Serial Ports                                                         | 26 |

|------------|----------------------------------------------------------------------|----|

| 2.7.5      | Gigabit Ethernet                                                     | 27 |

| 2.7.6      | SATA Interfaces                                                      | 27 |

| 2.7.7      | Debug Interface                                                      | 27 |

| 2.7.8      | CompactPCI Interface                                                 | 27 |

| 2.7.8.1    | Board Functionality when Installed in System Slot                    | 27 |

| 2.7.8.2    | Board Functionality when Installed in Peripheral Slot (Passive Mode) |    |

| 2.7.8.3    | Front/Rear I/O Configuration                                         |    |

| 2.7.8.4    | Board Insertion / Replacement under Power                            |    |

| 2.7.8.5    | Power Ramping                                                        |    |

| 2.7.8.6    | ENUM# Interrupt                                                      |    |

| 2.7.9      | CompactPCI Connectors J1 and J2                                      |    |

| 2.7.9.1    | CompactPCI Connector Keying                                          |    |

| 2.7.9.2    | CompactPCI Connectors J1 and J2 Pinouts                              |    |

| 2.7.9.3    | Optional Rear I/O Interface                                          |    |

| 2.7.9.4    | Rear I/O Pin Description                                             | 35 |

| 3          | Configuration                                                        | 40 |

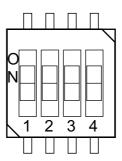

| 3.1        | DIP Switch Configuration                                             | 40 |

| 3.2        | System Write Protection                                              |    |

| 3.3        | CP3010-SA-Specific Registers                                         | 41 |

| 3.3.1      | Write Protection Register (WPROT)                                    | 42 |

| 3.3.2      | Reset Status Register (RSTAT)                                        | 43 |

| 3.3.3      | Board ID High-Byte Register (BIDH)                                   | 44 |

| 3.3.4      | Geographic Addressing Register (GEOAD)                               | 44 |

| 3.3.5      | Watchdog Timer Control Register (WTIM)                               | 45 |

| 3.3.6      | Board ID Low-Byte Register (BIDL)                                    | 46 |

| 3.3.7      | LED Configuration Register (LCFG)                                    | 46 |

| 3.3.8      | LED Control Register (LCTRL)                                         | 47 |

| 3.3.9      | General Purpose Output Register (GPOUT)                              |    |

| 3.3.10     | General Purpose Input Register (GPIN)                                | 48 |

| 4          | Power Considerations                                                 | 49 |

| 4.1        | CP3010-SA Voltage Ranges                                             | 49 |

| 4.2        | Power Consumption                                                    |    |

| 5          | Thermal Considerations                                               | 51 |

| 5.1        | Operational Limits for the CP3010-SA                                 |    |

|            | -F                                                                   |    |

| 6          | CP3010-HDD Extension Module                                          |    |

| 6.1        | Overview                                                             |    |

| 6.2        | Technical Specifications                                             |    |

| 6.3        | CP3010-HDD Module Functional Block Diagram                           |    |

| 6.4<br>6.5 | Front Panel of the CP3010-SA with CP3010-HDD Module                  |    |

| n h        | CP3010-HDD Module Board Lavout                                       | 56 |

| 6.6     | Module Interfaces (Front Panel and Onboard)    | 57 |

|---------|------------------------------------------------|----|

| 6.6.1   | CAN Interface                                  |    |

| 6.6.2   | Serial Port                                    | 57 |

| 6.6.3   | Gigabit Ethernet Interface                     | 57 |

| 6.6.4   | USB Interface                                  | 57 |

| 6.6.5   | Audio Interfaces                               | 57 |

| 6.6.6   | SATA Interface                                 | 57 |

| 7       | CP-RIO3-04 Rear Transition Module              | 58 |

| 7.1     | Overview                                       | 58 |

| 7.2     | Technical Specifications                       | 58 |

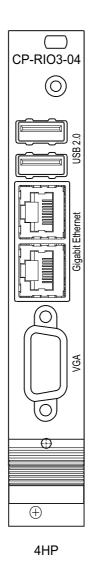

| 7.3     | CP-RIO3-04 Front Panels                        | 59 |

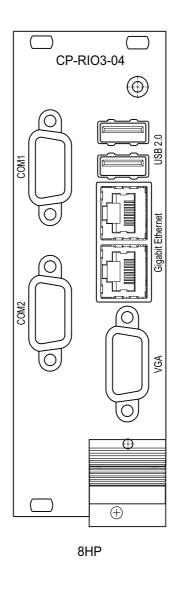

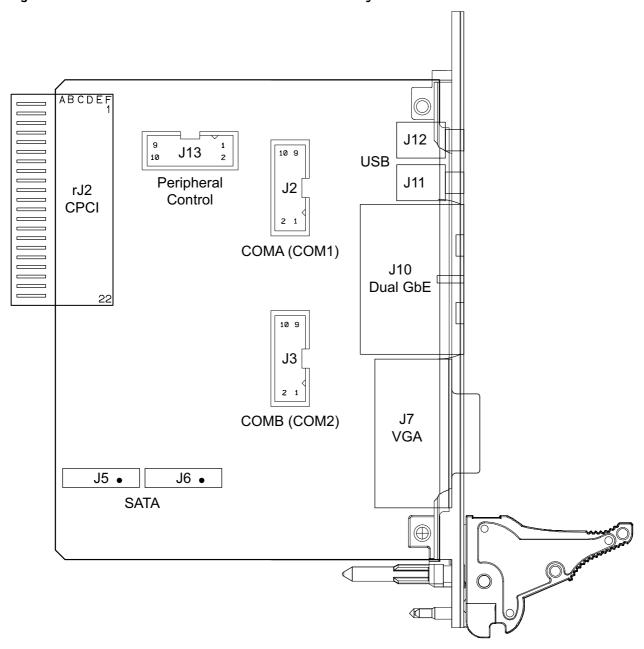

| 7.4     | CP-RIO3-04 Rear Transition Module Layout       | 60 |

| 7.5     | Module Interfaces                              | 62 |

| 7.5.1   | USB Interfaces                                 | 62 |

| 7.5.2   | VGA Interface                                  | 62 |

| 7.5.3   | Gigabit Ethernet Interface                     | 62 |

| 7.5.4   | COM Interface                                  | 62 |

| 7.5.5   | Peripheral Control Interface                   | 63 |

| 7.5.6   | SATA Interfaces                                | 63 |

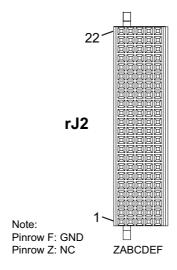

| 7.5.7   | Rear I/O Interface on CompactPCI Connector rJ2 | 64 |

| 8       | Installation                                   | 66 |

| 8.1     | Safety                                         | 66 |

| 8.2     | General Instructions on Usage                  | 66 |

| 8.3     | Board Installation                             | 66 |

| 8.3.1   | Standard Board Insertion                       | 67 |

| 8.3.2   | Standard Board Removal                         | 67 |

| 8.4     | CFast Card Installation                        | 68 |

| 8.5     | Rear Transition Module Installation            | 68 |

| 8.6     | Battery Replacement                            | 68 |

| 9       | uEFI BIOS                                      | 69 |

| 9.1     | Starting the uEFI BIOS Setup Program           | 69 |

| 9.2     | Setup Menus                                    |    |

| 9.2.1   | Main Setup Menu                                | 70 |

| 9.2.2   | Advanced Setup Menu                            | 71 |

| 9.2.3   | Security Setup Menu                            | 72 |

| 9.2.3.1 | Remember the Password                          | 72 |

| 9.2.4   | Boot Setup Menu                                | 73 |

| 9.2.5   | Exit Setup Menu                                | 73 |

| 9.3     | The uEFI Shell                                 | 74 |

| 9.3.1   | Introduction, Basic Operation                  | 74 |

| 9.3.1.1 | Entering the uEFI Shell                        | 74 |

| 9.3.1.2 | Exiting the uEFI Shell                         | 74 |

| 9.3.2   | Kontron-Specific uEFI Shell Commands           |    |

| 9.4     | uEFI Shell Scripting                              | 76 |

|---------|---------------------------------------------------|----|

| 9.4.1   | Startup Scripting                                 | 76 |

| 9.4.2   | Create a Startup Script                           | 76 |

| 9.4.3   | Examples of Startup Scripts                       | 77 |

| 9.4.3.1 | Execute Shell Script on Other Harddrive           | 77 |

| 9.4.3.2 | Enable Watchdog                                   | 77 |

| 9.4.3.3 | Handling the Startup Script in the SPI Boot Flash |    |

| 9.5     | Firmware Update                                   |    |

| 9.5.1   | Updating the uEFI BIOS                            |    |

| 9.5.1.1 | uEFI BIOS Fail-Over Mechanism                     | 79 |

| 9.5.1.2 | Updating Procedure                                | 79 |

| 9.5.1.3 | uEFI BIOS Recovery                                |    |

| 9.5.1.4 | Determining the Active Flash                      |    |

|         | <b>.</b>                                          |    |

# **Tables**

| 1  | CP3010-SA Main Specifications                                      | 16 |

|----|--------------------------------------------------------------------|----|

| 2  | Standards                                                          | 20 |

| 3  | Additional Standards for Boards with Extended Temperature Range    | 21 |

| 4  | Related Publications                                               | 21 |

| 5  | Features of the Processors Supported on the CP3010-SA              | 22 |

| 6  | System Status LEDs Function                                        | 24 |

| 7  | General Purpose LEDs Function                                      | 25 |

| 8  | POST Code Sequence                                                 | 25 |

| 9  | POST Code Example                                                  | 26 |

| 10 | CompactPCI Connector J1 System Slot Pinout                         | 30 |

| 11 | CompactPCI Connector J1 Peripheral Slot Pinout                     | 31 |

| 12 | CompactPCI Connector J2 Pinout (CP3010-SA Front I/O Vers.)         | 32 |

| 14 | CompactPCI Rear I/O Connector J3 Signals                           | 34 |

| 13 | Rear I/O CompactPCI Connector J2 Pinout (CP3010-SA Rear I/O Vers.) | 34 |

| 15 | GPIO Signal Description                                            | 35 |

| 16 | COMA and COMB Signal Description                                   | 35 |

| 17 | GPIO Signal Description                                            | 36 |

| 18 | VGA Signal Description                                             | 36 |

| 19 | Gigabit Ethernet Signal Description                                | 37 |

| 20 | SATA Signal Description                                            | 38 |

| 21 | USB Signal Description                                             | 38 |

| 22 | Power Supply and Power Management Signal Description               | 39 |

| 23 | DIP Switch SW1 Functionality                                       | 40 |

| 24 | CP3010-SA-Specific Registers                                       | 41 |

| 25 | Write Protection Register (WPROT)                                  | 42 |

| 26 | Reset Status Register (RSTAT)                                      | 43 |

| 27 | Board ID High-Byte Register (BIDH)                                 | 44 |

| 28 | Geographic Addressing Register (GEOAD)                             | 44 |

| 29 | Watchdog Timer Control Register (WTIM)                             | 45 |

| 30 | Board ID Low-Byte Register (BIDL)                                  | 46 |

| 31 | LED Configuration Register (LCFG)                                  | 46 |

| 32 | LED Control Register (LCTRL)                                       | 47 |

| 33 | General Purpose Output Register (GPOUT)                            | 48 |

| 34 | General Purpose Input Register (GPIN)                              | 48 |

| 35 | DC Operational Input Voltage Range                                 | 49 |

| 36 | CP3010-SA Power Consumption                                        | 50 |

| 37 | Power Consumption of CP3010-SA Accessories                         | 50 |

| 38 | CP3010-HDD Module Specifications                                   | 53 |

| 39 | Serial Port Connector J3 Pinout                                    | 57 |

| 40 | CP-RIO3-04 Rear Transition Module Specifications                   | 58 |

| 41 | Serial Port Connectors J2 (COMB) and J3 (COMA) Pinout              | 62 |

| 42 | Peripheral Control Connector J13 Pinout                            | 63 |

| 44 | Rear I/O Signal Description                                        | 65 |

| 43 | Rear I/O CompactPCI Connector rJ2 Pinout                           | 65 |

| 45 | Navigation                                                         | 69 |

| 46 | Main Setup Menu Sub-Screens and Functions                          | 70 |

| 47 | Advanced Setup Menu Sub-Screens and Functions | 71 |

|----|-----------------------------------------------|----|

| 48 | Security Setup Menu Functions                 | 72 |

| 49 | TPM Configuration Sub-Screen                  | 72 |

| 50 | Boot Priority Order                           | 73 |

| 51 | Exit Setup Menu Functions                     | 73 |

|    | Kontron-Specific uEFI Shell Commands          |    |

# **Figures**

| 1  | CP3010-SA Functional Block Diagram                       | 13 |

|----|----------------------------------------------------------|----|

| 2  | 4 HP CP3010-SA Front Panel                               | 14 |

| 3  | 4 HP CP3010-SA Board Layout (Top View)                   | 15 |

| 4  | 4 HP CP3010-SA Board Layout (Bottom View)                | 15 |

| 5  | CPCI Connectors J1/J2                                    | 29 |

| 6  | DIP Switch SW1                                           | 40 |

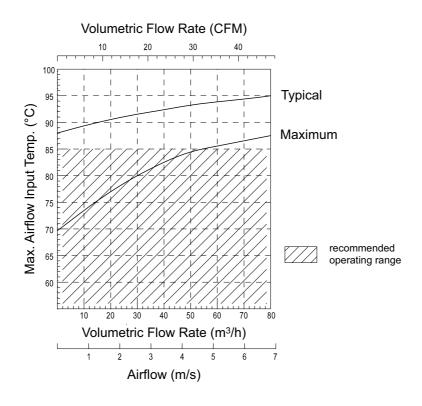

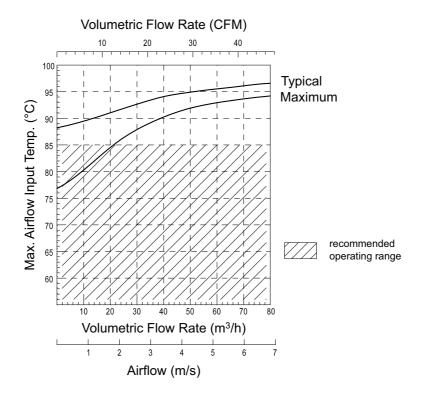

| 7  | CP3010-SA with Intel® Atom™ E3845, 1.91 GHz              | 52 |

| 8  | CP3010-SA with Intel® Atom™ E3827, 1.75 GHz              | 52 |

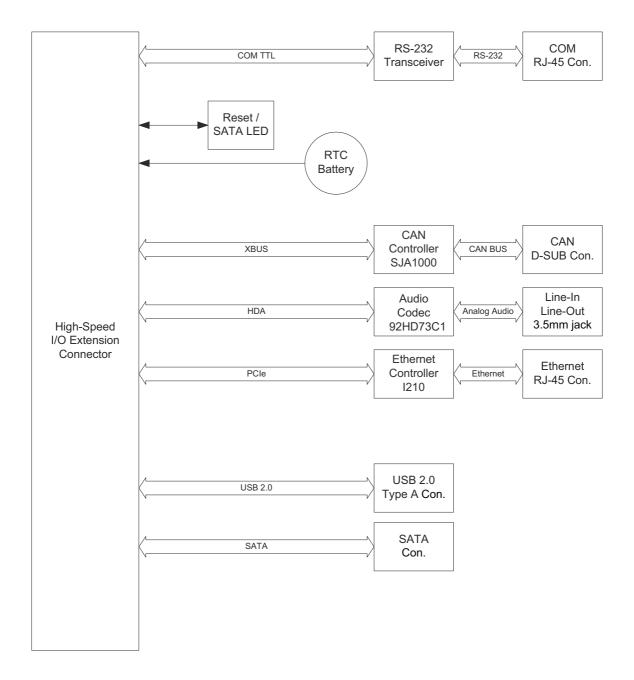

| 9  | CP3010-HDD Module Functional Block Diagram               | 55 |

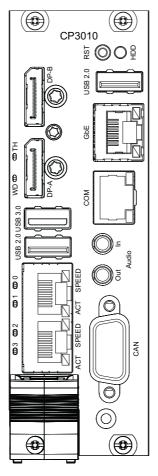

| 10 | Front Panel of the 8 HP CP3010-SA with CP3010-HDD Module | 56 |

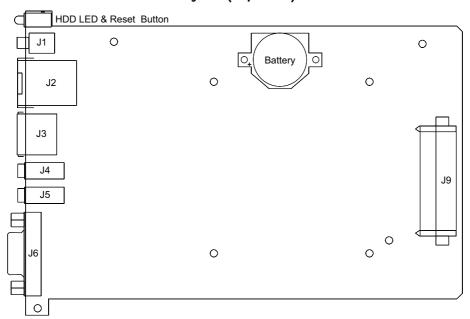

| 11 | CP3010-HDD Module Board Layout (Top View)                | 56 |

| 12 | Serial Port Connector J3                                 | 57 |

| 13 | CP-RIO3-04 4HP and 8HP Front Panels                      | 59 |

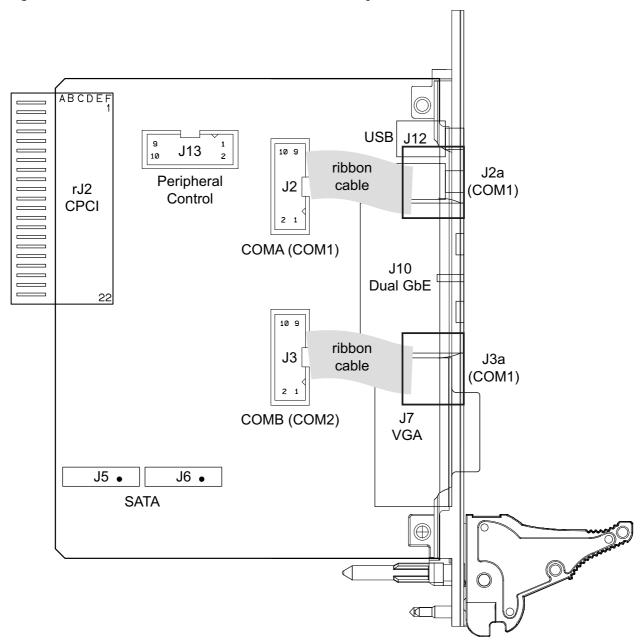

| 14 | 4HP CP-RIO3-04 Rear Transition Module Layout             | 60 |

| 15 | 8HP CP-RIO3-04 Rear Transition Module Layout             | 61 |

| 16 | Rear I/O CompactPCI Connector rJ2                        | 64 |

|    |                                                          |    |

### Warranty

This Kontron product is warranted against defects in material and workmanship for the warranty period from the date of shipment. During the warranty period, Kontron will at its discretion decide to repair or replace defective products.

Within the warranty period, the repair of products is free of charge as long as warranty conditions are observed.

The warranty does not apply to defects resulting from improper or inadequate maintenance or handling by the buyer, unauthorized modification or misuse, operation outside of the product's environmental specifications or improper installation or maintenance.

Kontron will not be responsible for any defects or damages to other products not supplied by Kontron that are caused by a faulty Kontron product.

### **Proprietary Note**

This document contains information proprietary to Kontron. It may not be copied or transmitted by any means, disclosed to others, or stored in any retrieval system or media without the prior written consent of Kontron or one of its authorized agents.

The information contained in this document is, to the best of our knowledge, entirely correct. However, Kontron cannot accept liability for any inaccuracies or the consequences thereof, or for any liability arising from the use or application of any circuit, product, or example shown in this document.

Kontron reserves the right to change, modify, or improve this document or the product described herein, as seen fit by Kontron without further notice.

### **Trademarks**

This document may include names, company logos and trademarks, which are registered trademarks and, therefore, proprietary to their respective owners.

### **Environmental Protection Statement**

This product has been manufactured to satisfy environmental protection requirements where possible. Many of the components used (structural parts, printed circuit boards, connectors, batteries, etc.) are capable of being recycled.

Final disposition of this product after its service life must be accomplished in accordance with applicable country, state, or local laws or regulations.

### 1 Introduction

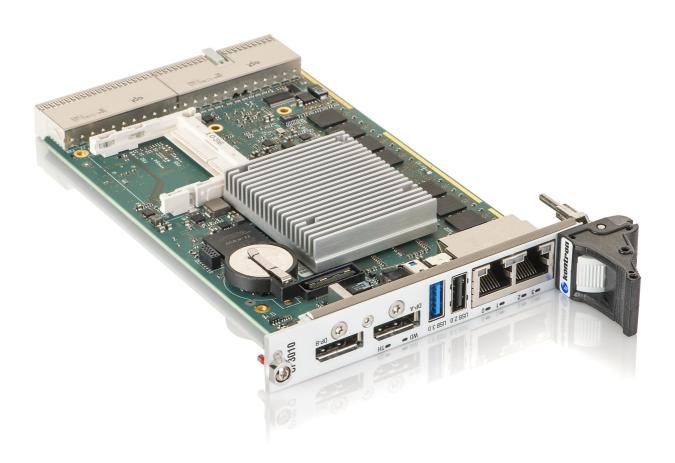

### 1.1 Board Overview

The CP3010-SA is a highly integrated, low-power, 3U CompactPCI® CPU board designed to support the Intel® Atom™ processors E3845 and E3827 with a maximum of quad-core 1.91 GHz processing performance. Even though the board design is based on the Atom™ technology, performance levels of former Core™2 Duo platforms can be reached. Further, the built-in graphics core now features Intel® HD Graphics Technology offering an outstanding increase in graphics performance compared to previous Atom™ designs.

Memory demanding applications can make use of up to 8 GB soldered DDR3L SDRAM memory running at 1333 MHz. For onboard data storage, the CP3010-SA offers a CFast option or a soldered SATA Flash and, on the 8HP extension module, an HDD/SSD option. On the system side, the CP3010-SA supports a PCI 32-bit, 33 MHz (66 MHz on request) CompactPCI® interface enabling the peripheral mode feature.

Using the latest Atom™ technology, the board offers a very low TDP (thermal design power) value. This feature, in conjunction with the special heat sink design, makes the CP3010-SA a perfect fit for all systems and applications where cooling by fans is not desired or not possible. As a result, operation in temperature ranges from -40°C up to +85°C is possible.

Designed with soldered processor and memory to handle even the toughest environmental conditions, the CP3010-SA can be used in industrial and mobile applications where motion, shock and vibration can typically be found. With respect to the transportation market, the CP3010-SA is fully EN50155-compliant.

The CP3010-SA comes with a comprehensive I/O feature set supporting interfaces such as DisplayPort, USB 3.0/2.0, Gigabit Ethernet, SATA, CAN, and RS-232 serial ports as well as the audio interfaces Line-In and Line-Out. Available as 4HP or 8HP version – optionally combined with rear I/O support – the CP3010-SA can be adapted to a wide range of application needs.

As a stable product based on Intel®'s embedded product line, the CP3010-SA ensures long-term availability. This eliminates the risk of unplanned design changes and unexpected expensive application modification. While minimizing deployment risks by providing a broad range of software support, the CP3010-SA eases the process of product integration and maximizes competitive advantages to meet time-to-market windows.

The board is offered with various Board Support Packages including Windows, VxWorks and Linux operating systems. For further information concerning the operating systems available for the CP3010-SA, please contact Kontron.

### 1.2 System Expansion Capabilities

### 1.2.1 CP3010-HDD Extension Module (8 HP)

The CP3010-HDD extension module for the 8 HP CP3010-SA version provides onboard support for a 2.5" HDD/SSD and various ports on the front panel, such as one USB 2.0 port, one COM port, one Gigabit Ethernet, one CAN port, and two audio interfaces (Line-In and Line-Out). For further information on the CP3010-HDD extension module, refer to Chapter 6.

#### 1.2.2 CP-RIO3-04 Rear Transition Module

The CP-RIO3-04 rear transition module has been designed for use with the CP3010-SA and provides comprehensive rear I/O functionality. For further information on the CP-RIO3-04 rear transition module, refer to Chapter 7.

### 1.3 Board Diagrams

The following diagrams provide additional information concerning board functionality and component layout.

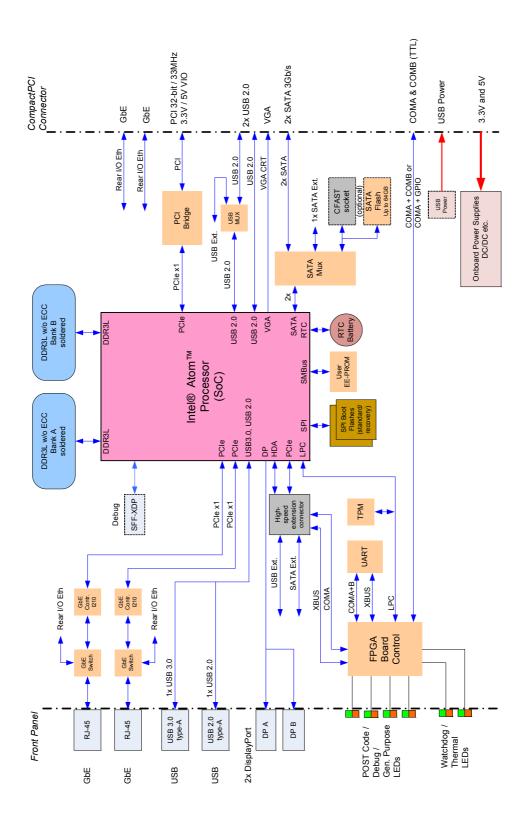

### 1.3.1 Functional Block Diagram

Figure 1: CP3010-SA Functional Block Diagram

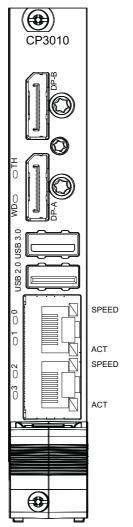

#### 1.3.2 Front Panel

Figure 2: 4 HP CP3010-SA Front Panel

### **System Status LEDs**

TH (red/green): Temperature Status WD (green): Watchdog Status

### **General Purpose LEDs**

LED3..0 (red/green/red+green): General Purpose/POST Code

**Note:** If the General Purpose LEDs 3..0 are lit red during boot-up,

a failure is indicated before the uEFI BIOS has started.

### **Integral Ethernet LEDs**

ACT (green): Ethernet Link/Activity

SPEED (orange): 1000BASE-T Ethernet Speed

SPEED (green): 100BASE-TX Ethernet Speed

SPEED (off) + ACT on: 10BASE-T Ethernet Speed

**Note:** For information regarding the front panel of the 8 HP CP3010-SA with a CP3010-HDD extension module, refer to Chapter 6.

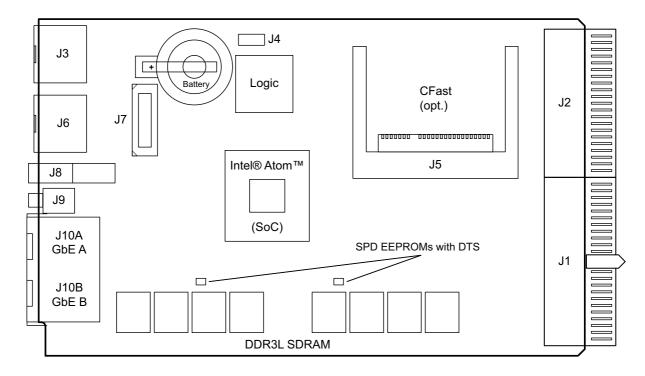

### 1.3.3 Board Layout

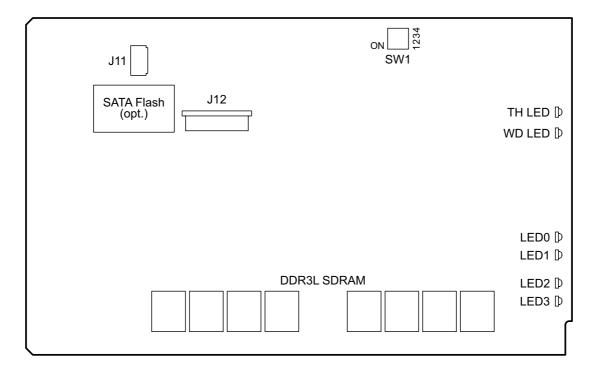

Figure 3: 4 HP CP3010-SA Board Layout (Top View)

Figure 4: 4 HP CP3010-SA Board Layout (Bottom View)

# 1.4 Technical Specification

Table 1: CP3010-SA Main Specifications

| FEATURES   |                     | SPECIFICATIONS                                                                         |  |

|------------|---------------------|----------------------------------------------------------------------------------------|--|

|            | СРИ                 | The CP3010-SA supports the following processors:                                       |  |

| SoC        |                     | » Quad-core Intel® Atom™ E3845, 1.91 GHz, 2 MB L2 cache                                |  |

|            |                     | » Dual-core Intel® Atom™ E3827, 1.75 GHz, 1 MB L2 cache                                |  |

|            | Graphics Controller | Intel® HD Graphics integrated in the processor with support for two independent        |  |

|            |                     | displays                                                                               |  |

|            | Main Memory         | Up to 8 GB, dual-channel DDR3L SDRAM memory without ECC running at 1333 MHz (soldered) |  |

| >          | Flash Memory        | Two 8 MB SPI boot flash chips for two separate uEFI BIOS images                        |  |

| Memory     | ,                   | SATA NAND flash (optional):                                                            |  |

| Σ<br>E     |                     | » Up to 64 GB soldered SATA NAND flash, or                                             |  |

|            |                     | » CFast card                                                                           |  |

|            | EEPROM              | EEPROM with 64 kbit                                                                    |  |

|            | CompactPCI          | CompactPCI interface:                                                                  |  |

|            |                     | » Compliant with CompactPCI Specification PICMG® 2.0 R 3.0                             |  |

|            |                     | » System master operation                                                              |  |

|            |                     | » 32-bit/33 MHz master interface (66 MHz on request)                                   |  |

|            |                     | » 3.3 V or 5 V (universal PCI interface)                                               |  |

|            |                     | » Support for up to seven peripheral slots (7x REQ/GNT signals)                        |  |

|            |                     | When installed in a peripheral slot, the CP3010-SA is isolated from the CompactPCI     |  |

|            |                     | bus. It receives power from the backplane and supports rear I/0.                       |  |

|            |                     | CP3010-SA removal under power:                                                         |  |

|            |                     | When installed in a peripheral slot, the CP3010-SA supports hot plugging on the        |  |

|            |                     | power interface through a dedicated power controller, but not on the PCI inter-        |  |

|            |                     | face.                                                                                  |  |

| ces        |                     | Hot swapping of peripheral boards controlled by the CP3010-SA:                         |  |

| Interfaces |                     | When installed in the system slot, the CP3010-SA supports the hot swapping of          |  |

| Inte       |                     | other boards. Individual clocks for each slot and Enum signal handling are in com-     |  |

|            |                     | pliance with the PICMG 2.1 Hot Swap Specification.                                     |  |

|            |                     | The CP3010-SA itself, however, is not hot swappable. When installed in the system      |  |

|            |                     | slot, the system must be powered down in order to replace the board.                   |  |

|            | Rear I/0            | The following interfaces are routed to the rear I/O connector J2:                      |  |

|            |                     | » COMA and COMB, or COMA and GPIO (all ports have 3.3V LVTTL signaling)                |  |

|            |                     | » General purpose signals: 5 x GPIs and 3 x GPOs                                       |  |

|            |                     | » 2 x USB 2.0                                                                          |  |

|            |                     | » 1 x CRT VGA                                                                          |  |

|            |                     | » 2 x Gigabit Ethernet                                                                 |  |

|            |                     | <ul><li>» 2 x SATA 3Gb/s</li><li>» System management signals</li></ul>                 |  |

|            |                     | » Input for 5V standby power                                                           |  |

|            |                     | » System write protection                                                              |  |

|            | <u> </u>            | 1                                                                                      |  |

Table 1: CP3010-SA Main Specifications (Continued)

| FEATURES   |                        | SPECIFICATIONS                                                                                                                                          |  |  |

|------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|            | DisplayPort            | Two DisplayPort interfaces (DVI/HDMI-capable through passive cable adapter) fo                                                                          |  |  |

|            |                        | connection to monitors                                                                                                                                  |  |  |

|            | Gigabit Ethernet       | Three 10 Base-T/100 Base-TX/1000 Base-T Gigabit Ethernet interfaces based on                                                                            |  |  |

|            |                        | three Intel® I210-IT Ethernet controllers:                                                                                                              |  |  |

|            |                        | » Two interfaces with Wake-on-LAN support and individually switchable to front I/O or rear I/O                                                          |  |  |

|            |                        | » One interface available on the high-speed I/O extension connector, J7, for the CP3010-HDD                                                             |  |  |

|            | USB                    | Four USB ports:                                                                                                                                         |  |  |

|            |                        | » One USB 3.0 port on the front $I/O$                                                                                                                   |  |  |

|            |                        | » One USB 2.0 port on the front I/O                                                                                                                     |  |  |

|            |                        | » Two USB 2.0 ports on the rear I/O CompactPCI interface, one of them switch-<br>able to the high-speed I/O extension connector, J7, for the CP3010-HDD |  |  |

|            | Serial                 | Two 16C550-compatible UARTs:                                                                                                                            |  |  |

| Interfaces |                        | » COMA available either on the rear I/O or on the high-speed I/O extension connector, J7, for the CP3010-HDD                                            |  |  |

| ıter       |                        | » COMB or GPIO available on the rear I/O only                                                                                                           |  |  |

| -          | SATA                   | Two SATA 3 Gb/s ports:                                                                                                                                  |  |  |

|            |                        | » One SATA port either onboard for the SATA Flash or the CFast card, or on the                                                                          |  |  |

|            |                        | rear I/O                                                                                                                                                |  |  |

|            |                        | » One SATA port either on the rear I/O or on the high-speed I/O extension connector, J7, for the CP3010-HDD                                             |  |  |

|            | I/O Extension          | I/O extension to 8 HP board version via the CP3010-HDD extension module:                                                                                |  |  |

|            | Interfaces             | » SATA 3 Gb/s for 2.5" HDD/SSD                                                                                                                          |  |  |

|            |                        | » USB 2.0                                                                                                                                               |  |  |

|            |                        | » Gigabit Ethernet                                                                                                                                      |  |  |

|            |                        | » COMA                                                                                                                                                  |  |  |

|            |                        | » Audio Line In                                                                                                                                         |  |  |

|            |                        | » Audio Line Out                                                                                                                                        |  |  |

|            |                        | » CAN                                                                                                                                                   |  |  |

|            |                        | » Reset button » HDD/SSD activity LED                                                                                                                   |  |  |

|            | Front Panel Connectors | 20 176                                                                                                                                                  |  |  |

|            | Tronc ranet connectors | <ul> <li>» DP: two standard DisplayPort connectors, J3 and J6</li> <li>» USB 3.0: one standard 9-pin, type A connector, J8</li> </ul>                   |  |  |

|            |                        | » USB 2.0: one standard 4-pin, type A connector, J9                                                                                                     |  |  |

|            |                        | » Ethernet: one standard dual RJ-45 connector, J10A/B                                                                                                   |  |  |

| ts         | Onboard Connectors     | » CompactPCI connectors, J1 and J2                                                                                                                      |  |  |

| Sockets    |                        | » CFast socket, J5 (optional)                                                                                                                           |  |  |

| Sc         |                        | » 60-pin, high-speed I/O extension connector, J7, for connection to the CP3010-<br>HDD extension module                                                 |  |  |

|            |                        | » JTAG connector, J4                                                                                                                                    |  |  |

|            |                        | » XDP-SFF (debug) connector, J12                                                                                                                        |  |  |

|            |                        | » SPI extension connector, J11                                                                                                                          |  |  |

Table 1: CP3010-SA Main Specifications (Continued)

| FEATURES        |                    | SPECI                                                                                                                                               | FICATIONS                                                      |  |

|-----------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

|                 | Front Panel LEDs   | System Status LEDs:                                                                                                                                 |                                                                |  |

| S               |                    | <pre>» TH (red/green):</pre>                                                                                                                        | Temperature Status                                             |  |

|                 |                    | » WD (green):                                                                                                                                       | Watchdog Status                                                |  |

| tche            |                    | General Purpose LEDs:                                                                                                                               |                                                                |  |

| LEDs/Switches   |                    | <pre>» LED30 (red/green/red+green):</pre>                                                                                                           | General Purpose/POST Code                                      |  |

| Ds/             |                    | Ethernet LEDs:                                                                                                                                      |                                                                |  |

| 쁘               |                    | » ACT (green):                                                                                                                                      | Network/Link Activity                                          |  |

|                 |                    | <pre>» SPEED (green/orange):</pre>                                                                                                                  | Network Speed                                                  |  |

|                 | DIP Switch         | One DIP switch, SW1, for board configu                                                                                                              | ration                                                         |  |

|                 | Real Time Clock    | Real-time clock with 242 Byte CMOS RA                                                                                                               | M; battery-backup available                                    |  |

| Timer           | Watchdog Timer     | Software-configurable, two-stage Watc                                                                                                               | hdog with programmable timeout ranging                         |  |

| Ë               |                    | from 125 ms to 4096 s in 16 steps                                                                                                                   |                                                                |  |

|                 |                    | Serves for generating IRQ or hardware reset                                                                                                         |                                                                |  |

| ent             | Thermal Management | CPU and board overtemperature protection is provided by:                                                                                            |                                                                |  |

| gem             |                    | » Up to four Digital Thermal Sensor                                                                                                                 | , ,                                                            |  |

| Sys. Management |                    | » One DTS for the Bus Interface Uni                                                                                                                 | t (BIU) within the SoC<br>PROMs near to the DDR3L memory banks |  |

| Σ.              |                    | <ul> <li>Iwo DIS integrated in the SPD EEF</li> <li>Specially designed heat sinks</li> </ul>                                                        | roms hear to the DDR3L memory banks                            |  |

| Sys             |                    | " specially designed near sinks                                                                                                                     |                                                                |  |

| ity             | TPM                | , , ,                                                                                                                                               | enhanced hardware- and software-based                          |  |

| Security        |                    | data and system security                                                                                                                            |                                                                |  |

| S               | uEFI BIOS          | Phoenix SecureCore TianeIM (SCT) PIOS fi                                                                                                            | rmware based on the uEFI Specification and                     |  |

|                 | ueri bios          | the Intel Platform Innovation Framewo                                                                                                               | -                                                              |  |

|                 |                    | » LAN boot capability for diskless systems (standard PXE)                                                                                           |                                                                |  |

|                 |                    | <ul> <li>LAN boot capability for diskless systems (standard PAE)</li> <li>Redundant image; fail-safe recovery in case of a damaged image</li> </ul> |                                                                |  |

|                 |                    | _                                                                                                                                                   | the SPI boot flash (battery only required for                  |  |

| are             |                    | the RTC)                                                                                                                                            | , , ,                                                          |  |

| Software        |                    | » Compatibility Support Module (CS based on Phoenix SCT3                                                                                            | M) providing legacy BIOS compatibility                         |  |

|                 |                    | » Command shell for diagnostics an                                                                                                                  | _                                                              |  |

|                 |                    | » uEFI Shell commands executable ronment (open interface)                                                                                           | from mass storage device in a pre-OS envi-                     |  |

|                 | Operating Systems  | There are various operating systems av                                                                                                              | ailable for the CP3010-SA. For further infor-                  |  |

|                 |                    | mation, please contact Kontron.                                                                                                                     |                                                                |  |

Table 1: CP3010-SA Main Specifications (Continued)

| FEATURES                                |                   | SPECIFICATIONS                                                                                                                                                                |  |  |

|-----------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                         | Power Consumption | See Chapter 4 for details.                                                                                                                                                    |  |  |

|                                         | Temperature Range | Operational: 0°C to +60°C Standard (depending on the airflow in the system)                                                                                                   |  |  |

|                                         |                   | -40°C to +85°C Extended (depending on the airflow in the system)                                                                                                              |  |  |

|                                         |                   | Storage: -40°C to +85°C Without hard disk and without battery                                                                                                                 |  |  |

|                                         | Battery           | 3.0V lithium battery for RTC; Battery type: UL-recognized CR2025                                                                                                              |  |  |

| General                                 |                   | Temperature ranges: Operational (load): -20°C to +70°C typical (refer to the battery manufacturer's specifications for exact range) Storage (no load): -40°C to +70°C typical |  |  |

|                                         | Climatic Humidity | 93% RH at 40 °C, non-condensing (acc. to IEC 60068-2-78)                                                                                                                      |  |  |

|                                         | Dimensions        | 100 mm x 160 mm                                                                                                                                                               |  |  |

|                                         |                   | 3U, 4 HP, CompactPCI-compliant form factor                                                                                                                                    |  |  |

| Board Weight 4 HP CP3010-SA with heat s |                   | 4 HP CP3010-SA with heat sink (without CFast card): 243 grams                                                                                                                 |  |  |

Note:

For information regarding the front panel of the 8 HP CP3010-SA with a CP3010-HDD extension module, refer to Chapter 6.

### 1.5 Standards

This product complies with the requirements of the following standards.

Table 2: Standards

| ТҮРЕ          | ASPECT                | STANDARD                             | REMARKS                            |

|---------------|-----------------------|--------------------------------------|------------------------------------|

| CE            | Emission              | EN 55011, EN 61000-6-4, EN 50155,    |                                    |

|               |                       | EN 50121-3-2 (Class B)               |                                    |

|               | Immunity              | EN 50155, EN 61000-6-2, EN 50121-3-2 |                                    |

|               | Electrical Safety     | EN 60950-1                           |                                    |

| Mechanical    | Mechanical Dimensions | IEEE 1101.10                         |                                    |

| Environmental | Climatic Humidity     | IEC 60068-2-78 (see note below)      |                                    |

|               | WEEE                  | Directive 2002/96/EC                 | Waste electrical and electronic    |

|               |                       | equipment                            |                                    |

|               | RoHS 2                | Directive 2011/65/EU                 | Restriction of the use of certain  |

|               |                       |                                      | hazardous substances in electri-   |

|               |                       |                                      | cal and electronic equipment       |

|               | Operating Vibration   | IEC 60068-2-6                        | Test parameters:                   |

|               |                       |                                      | 10-300 [Hz] frequency range        |

|               |                       |                                      | 5 [g] acceleration                 |

|               |                       |                                      | 1 [oct/min] sweep rate             |

|               |                       |                                      | 10 cycles/axis                     |

|               |                       |                                      | 3 directions                       |

|               | Operating Shocks      | IEC 60068-2-27                       | Test parameters:                   |

|               |                       |                                      | 30 [g] acceleration                |

|               |                       |                                      | 12 [ms] shock duration half sine   |

|               |                       |                                      | 3 shocks per direction (total: 18) |

|               |                       |                                      | 18 directions                      |

|               |                       |                                      | 5 [s] recovery time                |

|               | Operating Bumps       | IEC 60068-2-27                       | Test parameters:                   |

|               |                       |                                      | 15 [g] acceleration                |

|               |                       |                                      | 11 [ms] shock duration half sine   |

|               |                       |                                      | 500 shocks per direction           |

|               |                       |                                      | 6 directions                       |

|               |                       |                                      | 1 [s] recovery time                |

### Note:

Customers desiring to perform further environmental testing of the CP3010-SA must contact Kontron for assistance prior to performing any such testing.

Boards **without conformal coating** must not be exposed to a change of temperature which can lead to condensation. Condensation may cause irreversible damage, especially when the board is powered up again.

Kontron does not accept any responsibility for damage to products resulting from destructive environmental testing.

Furthermore, boards with extended temperature range comply with the following standards as well.

Table 3: Additional Standards for Boards with Extended Temperature Range

| ТҮРЕ          | ASPECT              | STANDARD          | REMARKS                                           |

|---------------|---------------------|-------------------|---------------------------------------------------|

| Thermal       | Operating Low       | IEC 60068-2-1     | Test parameters:                                  |

|               | Temperature         | Test Ad: Cold     | -40 [°C] ± 2 [°C]                                 |

|               | Railway TX          |                   | 16 [h] duration                                   |

|               |                     |                   | 1 cycle                                           |

|               |                     |                   | 1 [h] recovery (0.5 °C/min)                       |

|               | Operating High      | IEC 60068-2-2     | Test parameters:                                  |

|               | Temperature         | Test Bd: Dry Heat | +85[°C] ± 2[°C]                                   |

|               | Railway TX          |                   | 16 [h] duration                                   |

|               |                     |                   | 1 cycle                                           |

| Environmental | Operating Vibration | IEC 61000-2-64    | Test parameters:                                  |

|               | Railway Category 1, | Test Fh           | 5-150 [Hz] frequency range                        |

|               | Class B             |                   | ASD Spectrum [(m/s²)²/f] intensity of random      |

|               |                     |                   | vibration signal vs. frequency for X, Y, Z        |

|               |                     |                   | 1.00-0.45-0.70 [m/s²] rms                         |

|               |                     |                   | max. 10 [min] duration for each direction X, Y, Z |

|               | Operating Shocks    | IEC 60068-2-27    | Test parameters:                                  |

|               | Railway Category 1, |                   | 30-30-50 [m/s²] acceleration x-y-z                |

|               | Class B             |                   | 30-30-50 [ms] recovery time x-y-z                 |

|               |                     |                   | 3 shocks per direction (total: 18)                |

|               |                     |                   | 18 shocks                                         |

### 1.6 Related Publications

The following publications contain information relating to this product.

**Table 4: Related Publications**

| PRODUCT              | PUBLICATION                                                               |

|----------------------|---------------------------------------------------------------------------|

| CompactPCI Systems   | PICMG® 2.0, Rev. 3.0 CompactPCI® Specification                            |

| CFast                | CFast Specification Revision 1.1                                          |

| Platform Firmware    | Unified Extensible Firmware Interface (uEFI) specification, version 2.3.1 |

| All Kontron products | Product Safety and Implementation Guide, ID 1021-9142                     |

## 2 Functional Description

#### 2.1 Processor

The CP3010-SA supports the Intel® Atom™ E3845, and the Intel® Atom™ E3827 processors.

Table 5: Features of the Processors Supported on the CP3010-SA

| FEATURE                         | Intel® Atom™ E3845,<br>1.91 GHz | Intel® Atom™ E3827,<br>1.75 GHz |

|---------------------------------|---------------------------------|---------------------------------|

| Processor Cores                 | four                            | two                             |

| Processor Base Frequency        | 1.91 GHz                        | 1.75 GHz                        |

| SpeedStep®                      | supported                       | supported                       |

| L1 cache per core               | 56 kB                           | 56 kB                           |

| L2 cache                        | 2 x 1 MB                        | 2 x 512 kB                      |

| DDR3L Memory                    | up to 8 GB / 1333 MHz           | up to 8 GB / 1333 MHz           |

| Graphics Base Frequency         | 542 MHz                         | 542 MHz                         |

| Graphics Max. Dynamic Frequency | 792 MHz                         | 792 MHz                         |

| Thermal Design Power            | 10 W                            | 8 W                             |

For further information about the processors used on the CP3010-SA, please visit the Intel website. For further information concerning the suitability of other Intel processors for use with the CP3010-SA, please contact Kontron.

### 2.1.1 Integrated Processor Graphics Controller

The Intel® Atom™ processor includes a highly integrated processor graphics controller delivering high-performance 3D, 2D graphics capabilities. The integrated processor graphics controller has two independent display pipes allowing for dual display configurations. It provides support for either two digital ports capable of driving resolutions up to 2560 x 1600 pixels @ 60 Hz through DisplayPort, or one VGA port and one digital port capable of driving resolutions up to 2560 x 1600 pixels @ 60 Hz.

### 2.2 Memory

The CP3010-SA supports a soldered, dual-channel (144-bit), Double Data Rate (DDR3L) memory without Error Checking and Correcting (ECC) running at 1333 MHz. The available memory configuration can be either 4 GB or 8 GB.

However, when the internal graphics controller is enabled, the amount of memory available to applications is less than the total physical memory in the system. The SoC dynamically allocates the proper amount of system memory required by the operating system and the application.

### 2.3 Watchdog Timer

The CP3010-SA provides a Watchdog timer that is programmable for a timeout period ranging from 125 ms to 4096 s in 16 steps.

The Watchdog timer provides the following modes or operation:

- » Timer-only mode

- » Reset mode

- » Interrupt mode

- » Dual-stage mode

In dual-stage mode, a combination of both interrupt and reset is generated if the Watchdog is not serviced.

### 2.4 Battery

The CP3010-SA is provided with an UL-recognized CR2025, 3.0 V, "coin cell" lithium battery for the RTC. Power for the RTC may be provided either from the 4 HP/8 HP CP3010-SA or from the backplane/rear transition module, i.e. only one battery may be used at a time in a system. When a battery is installed, refer to the operational specifications of the battery as this determines the storage temperature of the CP3010-SA.

### 2.5 Flash Memory

The CP3010-SA provides flash interfaces for the uEFI BIOS and the SATA flash.

### 2.5.1 SPI Boot Flash for uEFI BIOS

The CP3010-SA provides two 8 MB SPI boot flashes for two separate uEFI BIOS images, a standard SPI boot flash and a recovery SPI boot flash. The switching mechanism for the uEFI BIOS recovery is controlled via the DIP switch SW1, switch 2. The SPI boot flash includes a hardware write protection option, which can be configured via the uEFI BIOS. If write protection is enabled, the SPI boot flash cannot be written to.

Note:

The uEFI BIOS code and settings are stored in the SPI boot flashes. Changes made to the uEFI BIOS settings are available only in the currently selected SPI boot flash. Thus, switching over to the other SPI boot flash may result in operation with different uEFI BIOS code and settings.

#### 2.5.2 SATA Flash

For flexible flash extension, the CP3010-SA provides either a CFast socket, J5, for a SATA 3Gb/s CFast memory card, or up to 64 GB soldered SLC-based NAND flash memory with built-in full hard disk emulation, up to 60 MB/s read rate, and up to 55 MB/s write rate.

**Note:** Write protection is available for both the CFast card and the soldered NAND flash. Please contact Kontron for further assistance if write protection is required.

#### 2.6 Trusted Platform Module 1.2

The CP3010-SA supports the Trusted Platform Module (TPM) 1.2. TPM1.2 is a security chip specifically designed to provide enhanced hardware- and software-based data and system security. TPM1.2 is based on the Atmel AT97SC3204 security controller and stores sensitive data such as encryption and signature keys, certificates and passwords, and is able to withstand software attacks to protect the stored information.

### 2.7 Board Interfaces

### 2.7.1 Front Panel LEDs

The CP3010-SA provides two system status LEDs, one temperature status LED (TH LED) and one Watchdog status LED (WD LED), as well as four General Purpose/POST code LEDs (LED3..0). Their functionality is described in the following chapters and reflected in the registers mentioned in Chapter 3, Configuration.

#### 2.7.1.1 System Status LEDs

Table 6: System Status LEDs Function

| LED    | COLOR     | STATE      | FUNCTION                                                                  |  |  |  |  |

|--------|-----------|------------|---------------------------------------------------------------------------|--|--|--|--|

| TH LED | red/green | Off        | Power failure                                                             |  |  |  |  |

|        |           | Green      | Board in normal operation                                                 |  |  |  |  |

|        |           | Red        | CPU operating temperature has exceeded its defined operating limit        |  |  |  |  |

|        |           | Red blinks | CPU temperature above 110°C (CPU has been shut off)                       |  |  |  |  |

|        |           |            | In this event, all General Purpose LEDs (LED30) are blinking red as well. |  |  |  |  |

| WD LED | red/green | OFF        | Watchdog inactive                                                         |  |  |  |  |

|        |           | Green      | Watchdog active, waiting to be triggered                                  |  |  |  |  |

|        |           | Red        | Watchdog expired                                                          |  |  |  |  |

#### Note:

If the TH LED flashes red at regular intervals, it indicates that the processor junction temperature has reached a level beyond which permanent silicon damage may occur and the processor has been shut off. To return to normal operation, the power must be switched off and then on again.

### 2.7.1.2 General Purpose LEDs

The General Purpose LEDs (LED3..0) are designed to indicate the boot-up POST code after which they are available to the application. If the LED3..0 are lit red during boot-up, a failure is indicated. In this event, please contact Kontron for further assistance.

The POST code is indicated during the boot-up phase. After boot-up, the LEDs indicate General Purpose or Port 80 signals, depending on the uEFI BIOS settings. The default setting after boot-up is General Purpose.

Table 7: General Purpose LEDs Function

| LED  | COLOR     | FUNCTION DURING BOOT-UP | FUNCTION DURING uEFI BIOS POST (if POST code config. is enabled) | FUNCTION<br>AFTER BOOT-UP                            |  |

|------|-----------|-------------------------|------------------------------------------------------------------|------------------------------------------------------|--|

| LED3 | red       | Power failure           |                                                                  | Canaral Durnasa ar Dart 90                           |  |

|      | green     |                         | uEFI BIOS POST bit 3 and bit 7                                   | General Purpose or Port 80  Default: General Purpose |  |

|      | red+green |                         |                                                                  | Derautt. Generat rurpose                             |  |

| LED2 | red       | CPU catastrophic error  | CPU catastrophic error                                           | Camaral Duranasa ar Daret 00                         |  |

|      | green     |                         | uEFI BIOS POST bit 2 and bit 6                                   | General Purpose or Port 80  Default: General Purpose |  |

|      | red+green |                         |                                                                  |                                                      |  |

| LED1 | red       | Hardware reset          |                                                                  | Camaral Duranasa ar Daret 90                         |  |

|      | green     |                         | uEFI BIOS POST bit 1 and bit 5                                   | General Purpose or Port 80  Default: General Purpose |  |

|      | red+green |                         |                                                                  | Derautt. Generat Furpose                             |  |

| LED0 | red       | uEFI BIOS boot failure  |                                                                  | Camaral Duranasa ar Daret 90                         |  |

|      | green     |                         | uEFI BIOS POST bit 0 and bit 4                                   | General Purpose or Port 80  Default: General Purpose |  |

|      | red+green |                         |                                                                  | - Delautt: General Purpose                           |  |

For further information regarding the configuration of the General Purpose LEDs, refer to Chapter 3.3.7, LED Configuration Register, and Chapter 3.3.8, LED Control Register.

**Note:** The bit allocation for Port 80 is the same as for the POST code.

### How to Read the 8-Bit POST Code

Due to the fact that only 4 LEDs are available and 8 bits must be displayed, the POST code output is multiplexed on the General Purpose LEDs.

Table 8: POST Code Sequence

| STATE | GENERAL PURPOSE LEDs                       |

|-------|--------------------------------------------|

| 0     | All LEDs are OFF; start of POST sequence   |

| 1     | High nibble                                |

| 2     | Low nibble; state 2 is followed by state 0 |

The following is an example of the General Purpose LEDs' operation if the POST configuration is enabled (see also Table 8, General Purpose LEDs Function).

Table 9: POST Code Example

|             | LED3    | LED2    | LED1    | LED0    | RESULT |

|-------------|---------|---------|---------|---------|--------|

| HIGH NIBBLE | off (0) | on (1)  | off (0) | off (0) | 0x4    |

| LOW NIBBLE  | off (0) | off (0) | off (0) | on (1)  | 0x1    |

| POST CODE   | 0x41    |         |         |         |        |

#### Note:

Under normal operating conditions, the General Purpose LEDs should not remain lit during boot-up. They are intended to be used only for debugging purposes. In the event that a General Purpose LED lights up during boot-up and the CP3010-SA does not boot, please contact Kontron for further assistance.

#### 2.7.2 USB Interfaces

The CP3010-SA provides four USB ports:

- » One USB 3.0 port on the front I/O

- » One USB 2.0 port on the front I/O

- » Two USB 2.0 ports on the rear I/O, one of them switchable to the high-speed I/O extension connector, J7, for the CP3010-HDD extension module

On the front panel, the CP3010-SA has one standard, type A, USB 3.0 connector, J8, and one standard, type A, USB 2.0 connector, J9.

### 2.7.3 DisplayPort Interfaces

The CP3010-SA provides two standard DisplayPort interfaces for connection to two monitors. The interfaces are implemented as standard DisplayPort connectors, J3 and J6, on the front panel.

#### 2.7.4 Serial Ports

The CP3010-SA provides two serial ports:

- » COMA available either on the CompactPCI rear I/O connector (3.3V LVTTL) or on the CP3010-HDD extension module

- » COMB on the CompactPCI rear I/O connector (3.3V LVTTL)

COMA and COMB are fully compatible with the 16C550 controller and include a complete set of hand-shaking and modem control signals. The COMA and COMB ports provide maskable interrupt generation. The data transfer on the COM ports is up to 115.2 kbit/s.

### 2.7.5 Gigabit Ethernet

The CP3010-SA board includes three 10Base-T/100Base-TX/1000Base-T Ethernet ports based on three Intel® I210-IT Ethernet controllers (two onboard and one on the CP3010-HDD extension module). All three controllers are connected to the x1 PCI Express interfaces of the Intel® Atom™ processor. Two Gigabit Ethernet interfaces are individually switchable between front I/O and rear I/O and provide Wake-on-LAN support. One interface is available on the high-speed I/O extension connector, J7, for the CP3010-HDD module.

Note:

In order to use the Wake-on-LAN feature, the power supply must not be switched off (+5V stand-by voltage cannot be used). The CP3010-SA does not turn off the main power supply after an operating system shutdown in order to support Wake-on-LAN.

Two of the Gigabit Ethernet interfaces are implemented as a standard RJ-45 Ethernet connectors, J10A/B on the front panel.

#### 2.7.6 SATA Interfaces

The CP3010-SA provides two SATA ports:

- » One SATA 3 Gb/s port either onboard for the SATA Flash or the CFast card, or on the Compact-PCI rear I/O interface

- » One SATA 3 Gb/s port either on the CompactPCI rear I/O interface or on the high-speed I/O extension connector, J7, for the CP3010-HDD extension modules

### 2.7.7 Debug Interface

The CP3010-SA provides several onboard options for hardware and software debugging, such as:

- » Four bicolor general purpose LEDs (LED0..3), which indicate hardware failures, uEFI BIOS POST codes and user-configurable outputs

- » One JTAG connector, J4, for programming the onboard logic

- » One XDP-SFF, processor JTAG connector, J12, for facilitating the debug and uEFI BIOS software development

#### 2.7.8 CompactPCI Interface

The CP3010-SA supports a flexible CompactPCI interface with a hot plug power interface (no PCI hot swap). In the system slot the PCI interface is in transparent mode, and in the peripheral slot the CompactPCI interface is isolated so that it cannot communicate with the CompactPCI bus. This mode is known as "passive mode".

#### 2.7.8.1 Board Functionality when Installed in System Slot

In a system slot, the CompactPCI interface is provided as 32-bit/33 MHz (66 MHz on request) PCI interface. The CP3010-SA supports up to seven peripheral slots through a CompactPCI backplane.

Note:

The CP3010-SA supports universal PCI V(I/O) signaling voltages with one common resistor configuration. For both 5V and 3.3 V PCI signaling voltages, 2.7 k $\Omega$  pull-up resistors are used.

### 2.7.8.2 Board Functionality when Installed in Peripheral Slot (Passive Mode)

In a peripheral slot, the board receives power but does not communicate on the CompactPCI bus; all CompactPCI signals are isolated.

### 2.7.8.3 Front/Rear I/O Configuration

The CP3010-SA is available in two versions:

- » CP3010-SA front I/O version

- » CP3010-SA rear I/O version

Please ensure that the correct version is stated on the order. If the CP3010-SA is ordered with rear I/O configuration, various I/O interfaces and signals are available via the CompactPCI connector J2, such as USB, SATA, GbE, VGA, and COM, as well as power and management signals. If the CP3010-SA is ordered with front I/O configuration, the I/O interfaces and signals mentioned above are isolated from the CompactPCI connector J2.

Note:

The CP3010-SA with front I/O configuration does not provide a 64-bit termination to the backplane via the CompactPCI connector J2. This is different than on previous boards such as CP307 or CP308 where 64-bit termination is provided.

### 2.7.8.4 Board Insertion / Replacement under Power

The following features are implemented on the CP3010-SA:

- » Power ramping

- » ENUM signal handling (hot swapping of peripheral boards)

Power ramping on the CP3010-SA provides the hot plug functionality on the power interface. The PCI signal interface does not provide hot swap functionality. No microswitch, no blue LED and no signal precharge are provided on the CP3010-SA.

The ENUM signal on the CP3010-SA allows for hot swapping of peripheral boards with hot swap capability when the CP3010-SA is installed in the system slot.

Note:

The CP3010-SA itself is not hot swappable when inserted in a system slot. When inserted in a peripheral slot, the CP3010-SA is hot pluggable.

#### 2.7.8.5 Power Ramping

On the CP3010-SA a special power controller is used to ramp up the onboard supply voltages. This is done to avoid transients on the +3.3V and +5V power supplies from the system. When the power supply is stable, the power controller generates an onboard reset to put the board into a defined state.

#### 2.7.8.6 ENUM# Interrupt

If the board is operated in the system slot, the ENUM signal is an input.

### 2.7.9 CompactPCI Connectors J1 and J2

The CP3010-SA provides two CompactPCI connectors, J1 and J2, with the following functionality:

- » J1:32-bit CompactPCI interface with PCI bus signals, arbitration, clock and power

- » J2: arbitration, clock and optionally rear I/O interface functionality

The CP3010-SA is designed for a CompactPCI bus architecture and the board is capable of driving up to seven CompactPCI slots with individual arbitration and clock signals.

The CompactPCI standard is electrically identical to the PCI local bus. However, these systems are enhanced to operate in rugged industrial environments and to support multiple slots.

### 2.7.9.1 CompactPCI Connector Keying

CompactPCI backplane connectors support guide lugs to ensure a correct polarized mating (3.3 V or 5 V V(I/0) coding).

The CP3010-SA supports universal (3.3 V and 5 V) PCI V(I/0) signaling voltages with one common termination resistor configuration. Therefore, the CP3010-SA can be inserted in both, 3.3 V and 5 V CompactPCI systems and provides itself no guide lug.

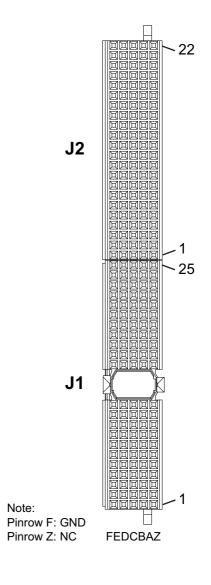

Figure 5: CPCI Connectors J1/J2

### 2.7.9.2 CompactPCI Connectors J1 and J2 Pinouts

The CP3010-SA is provided with two 2 mm x 2 mm pitch female CompactPCI bus connectors, J1 and J2.

Table 10: CompactPCI Connector J1 System Slot Pinout

| PIN   | Z  | A        | В             | С        | D      | E        | F   |

|-------|----|----------|---------------|----------|--------|----------|-----|

| 25    | NC | 5V       | REQ64#        | ENUM#    | 3.3V   | 5V       | GND |

| 24    | NC | AD[1]    | 5V            | V(I/0)   | AD[0]  | ACK64#   | GND |

| 23    | NC | 3.3V     | AD[4]         | AD[3]    | 5V     | AD[2]    | GND |

| 22    | NC | AD[7]    | GND           | 3.3V     | AD[6]  | AD[5]    | GND |

| 21    | NC | 3.3V     | AD[9]         | AD[8]    | M66EN  | C/BE[0]# | GND |

| 20    | NC | AD[12]   | GND           | V(I/0)   | AD[11] | AD[10]   | GND |

| 19    | NC | 3.3V     | AD[15]        | AD[14]   | GND    | AD[13]   | GND |

| 18    | NC | SERR#    | GND           | 3.3V     | PAR    | C/BE[1]# | GND |

| 17    | NC | 3.3V     | RSV           | RSV      | GND    | PERR#    | GND |

| 16    | NC | DEVSEL#  | PCIXCAP       | V(I/0)   | STOP#  | LOCK#    | GND |

| 15    | NC | 3.3V     | FRAME#        | IRDY#    | BDSEL# | TRDY#    | GND |

| 12-14 |    |          |               | Key Area |        |          |     |

| 11    | NC | AD[18]   | AD[17]        | AD[16]   | GND    | C/BE[2]# | GND |

| 10    | NC | AD[21]   | GND           | 3.3V     | AD[20] | AD[19]   | GND |

| 9     | NC | C/BE[3]# | NC            | AD[23]   | GND    | AD[22]   | GND |

| 8     | NC | AD[26]   | GND           | V(I/0)   | AD[25] | AD[24]   | GND |